De acordo com relatos, A Samsung Electronics produziu com sucesso um wafer funcional DRAM baseado na arquitetura 4F² pela primeira vez no mundo, rompendo o limite de encolhimento físico que a DRAM planar tradicional enfrenta há muito tempo. É relatado que em fevereiro deste ano, a Samsung demonstrou publicamente este protótipo DRAM de 16 Gb integrando a arquitetura 4F² pela primeira vez na conferência ISSCC 2026.

A Samsung concluiu a produção de wafer usando o processo 10a em março e confirmou a operação normal do wafer por meio de testes característicos. Essa conquista é a primeira prática mundial de integração de estrutura de célula 4F² e tecnologia de transistor de canal vertical (VCT).

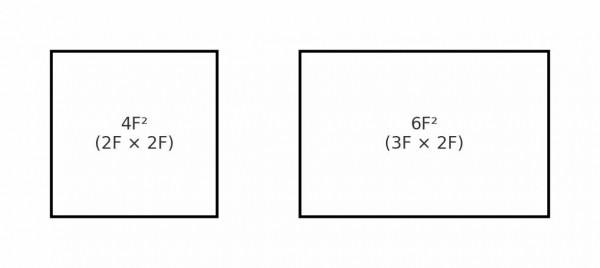

Tecnicamente, a arquitetura 4F² reduz a área unitária da DRAM tradicional de 6F² para uma estrutura quadrada 2F×2F, o que pode teoricamente aumentar a capacidade por unidade de área em 30% a 50%, levando em consideração as vantagens de velocidade e consumo de energia.

Para concretizar essa estrutura, a Samsung introduziu a tecnologia VCT para erguer verticalmente o canal do transistor e aumentar o comprimento do canal dentro da área limitada do chip, aliviando efetivamente o efeito de canal curto e os problemas de vazamento encontrados pelos transistores planares tradicionais durante o dimensionamento.

Por outro lado, a Samsung usa tecnologia de ligação de cobre híbrida entre wafers para separar o conjunto de células de memória e os circuitos periféricos em diferentes wafers e, em seguida, empilhá-los verticalmente para obter interconexão de ultra-alta densidade.

O material do canal também foi alterado do silício tradicional para óxido de índio-gálio-zinco (IGZO) para suprimir a corrente de fuga em células encolhidas.

No futuro, chips DRAM do mesmo tamanho poderão ser embalados com mais unidades. Espera-se que dispositivos terminais, como notebooks e smartphones finos e leves, alcancem maior capacidade de memória e transferência de dados mais rápida sob a premissa de tamanho pequeno e baixo consumo de energia.

A Samsung planejou um roteiro claro para isso – concluir o desenvolvimento de 10a DRAM em 2026, realizar testes de qualidade em 2027 e passar para a produção em massa em 2028.

SK Hynix planeja introduzir 4F²+VCT no nó 10b, enquanto a Micron mantém a rota de design existente. Os fabricantes chineses implantam diretamente DRAM 3D devido às restrições EUV.